Seuraat nyt käyttäjää

Virhe seurattaessa käyttäjää.

Tämä käyttäjä ei salli käyttäjien seurata häntä.

Seuraat jo tätä käyttäjää.

Jäsenyystasosi mahdollistaa vain 0 seurausta. Päivitä tästä.

Käyttäjän seuraaminen lopetettu onnistuneesti

Virhe poistettaessa käyttäjän seurantaa.

Olet onnistuneesti suositellut käyttäjää

Virhe suositeltaessa käyttäjää.

Jokin meni vikaan. Päivitä sivu ja yritä uudelleen.

Sähköposti vahvistettu onnistuneesti.

rawalpindi,

pakistan

Aika on tällä hetkellä 11:09 ip. täällä

Liittynyt lokakuuta 15, 2011

0 Suositukset

Elecguru011

@Elecguru011

0,0

0,0

83%

83%

rawalpindi,

pakistan

Ei saatavilla

Suoritetut työt

Ei saatavilla

Budjetin mukaisesti

Ei saatavilla

Aikataulussa

Ei saatavilla

Uudelleenpalkkausaste

Embedded Design Enigneer with expertise in FPGA and DSP Systems Engineering

Ota yhteyttä käyttäjään Elecguru011 työhösi liittyen

Kirjaudu sisään keskustellaksesi yksityiskohdista chatissa.

Portfolio

Portfolio

25Hz Transmitter Coil

25Hz Transmitter Coil

25Hz Transmitter Coil

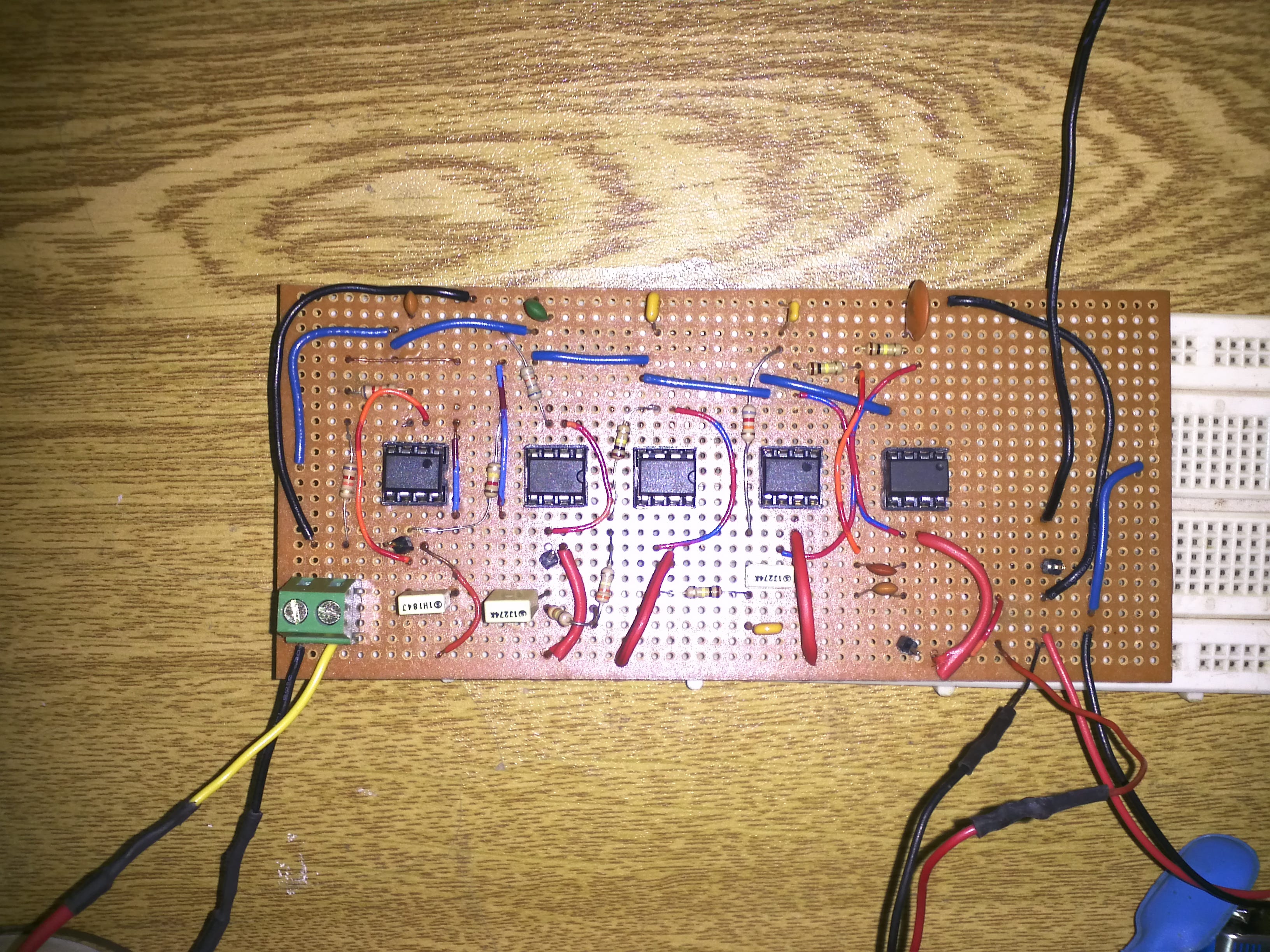

Sullen Key Filter

Sullen Key Filter

Sullen Key Filter

Sullen Key Filter

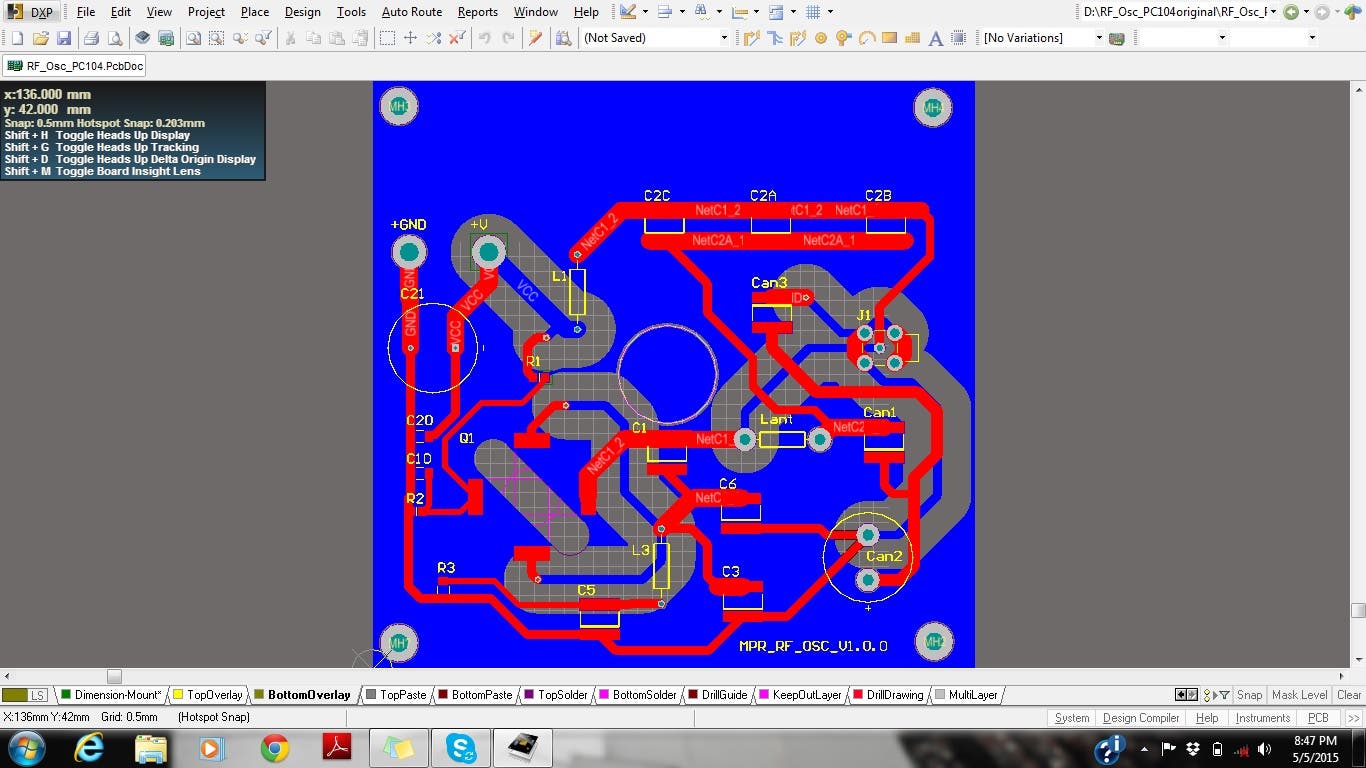

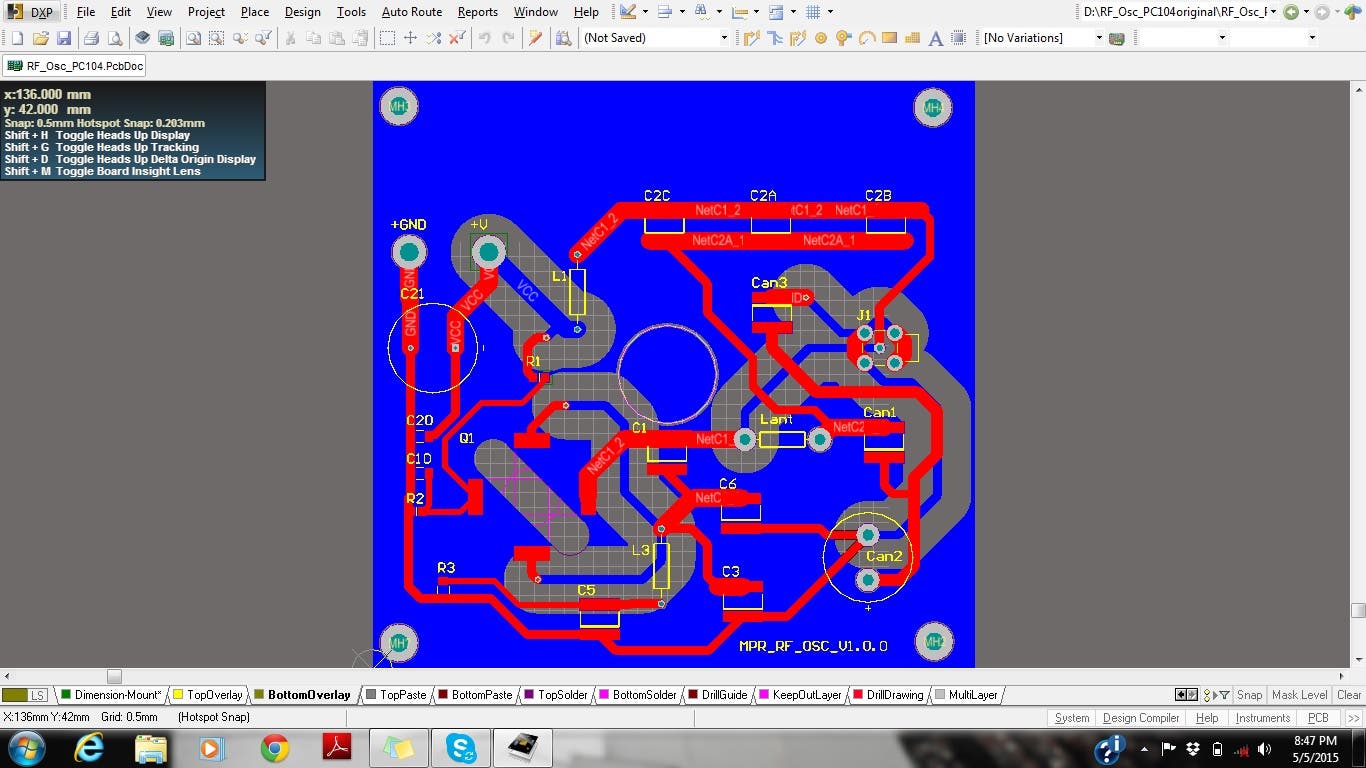

RF Oscillator

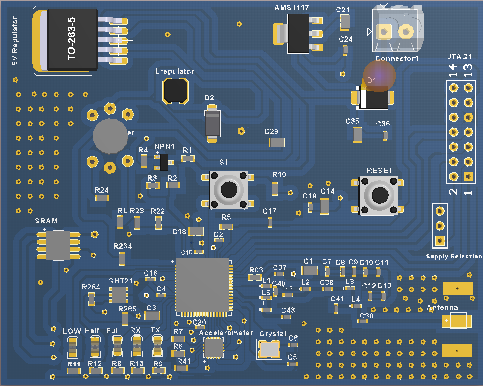

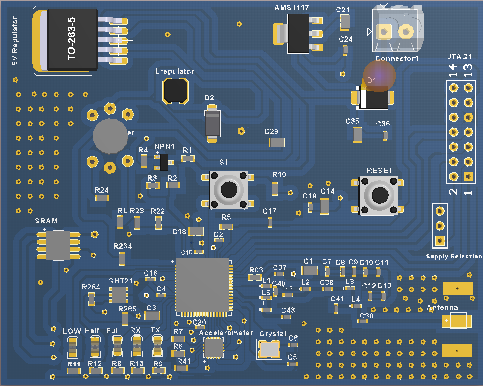

DASH-7 Wireless Board

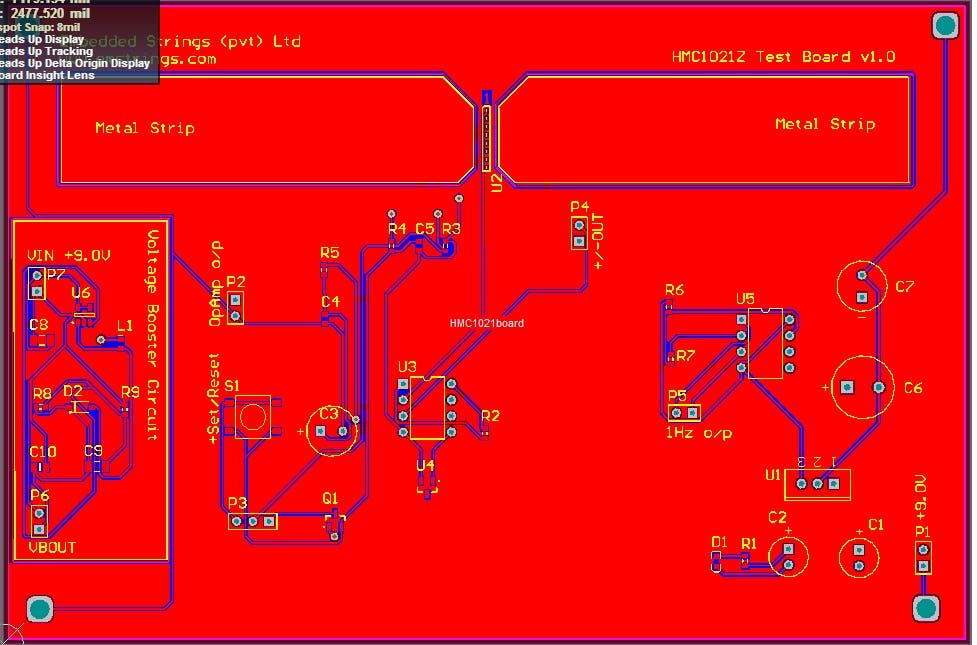

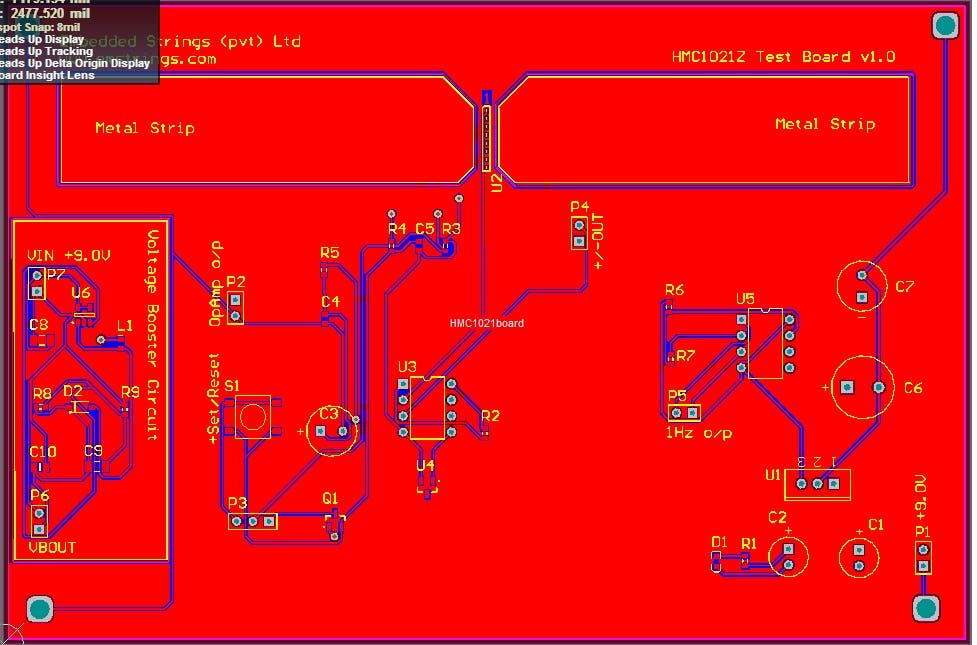

Altium PCB Design

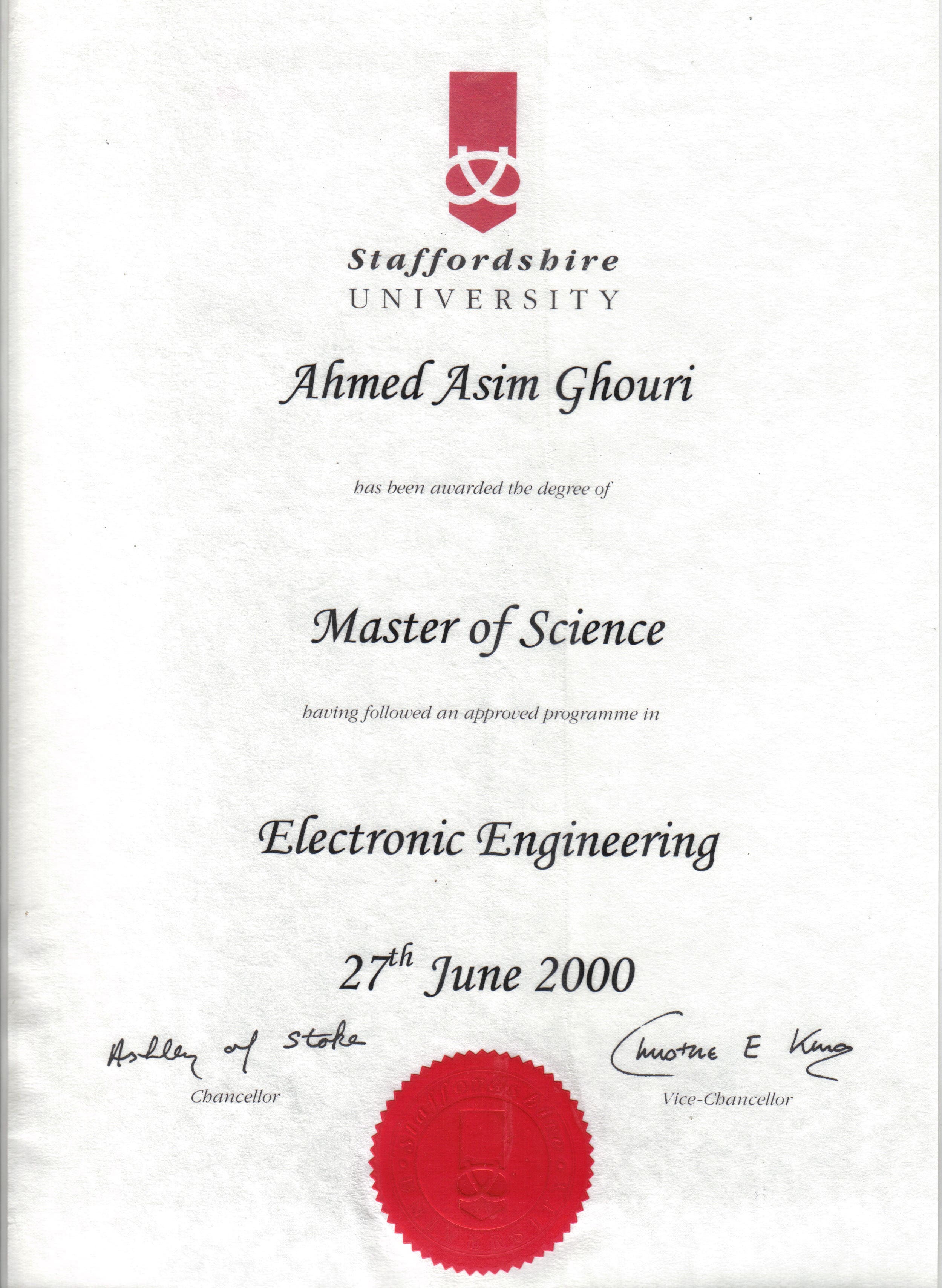

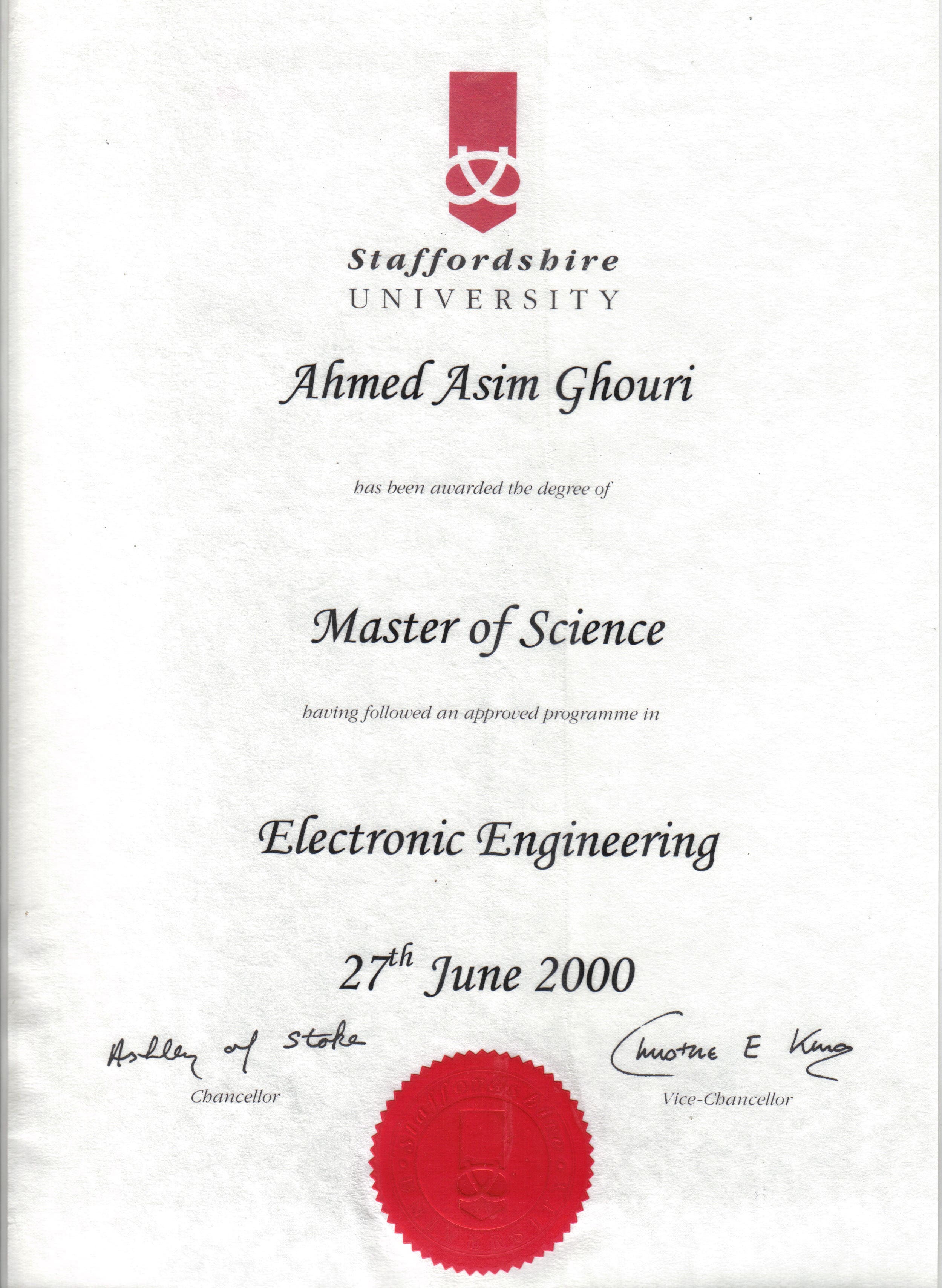

Masters of Electronics Engineering

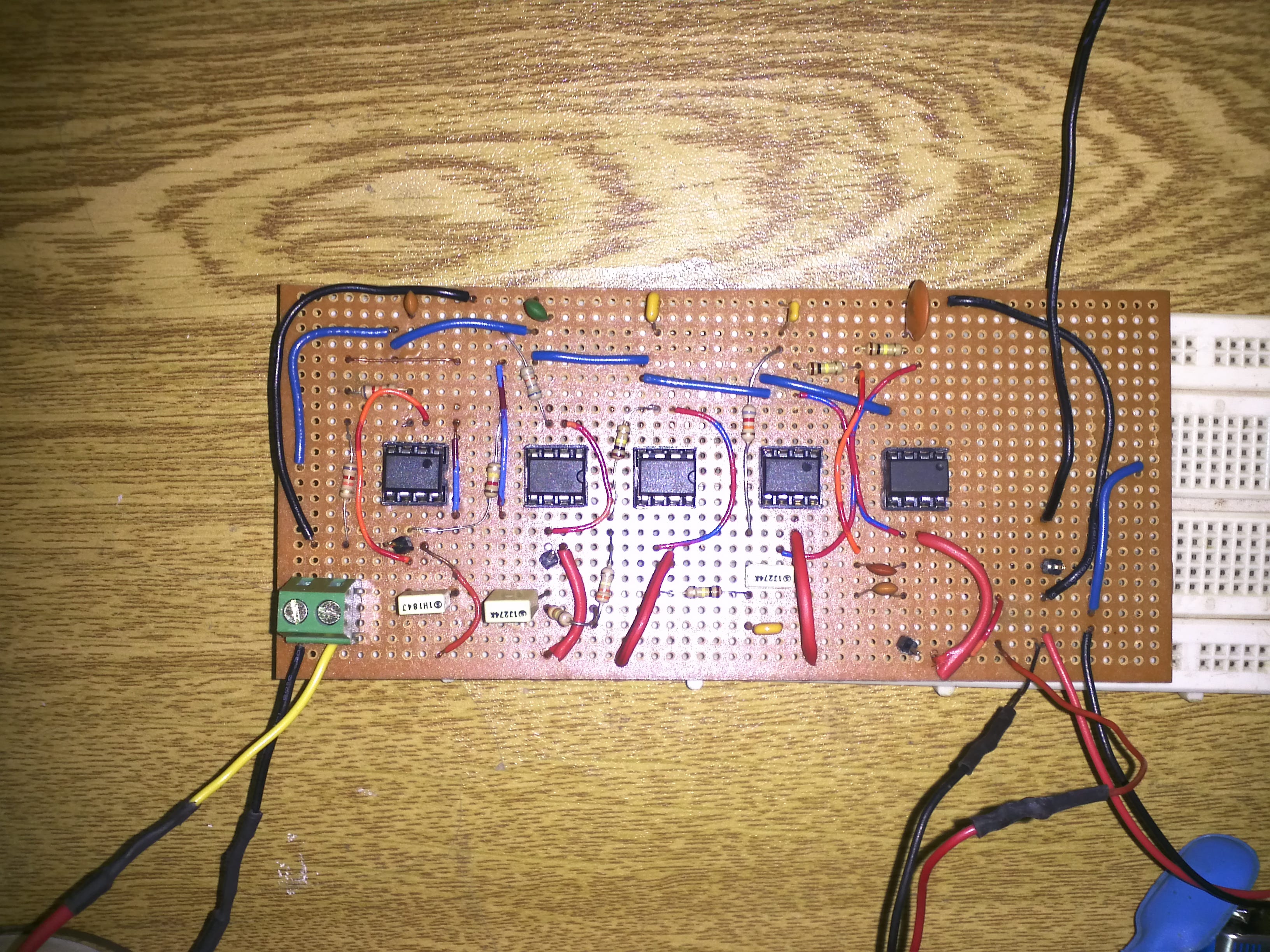

25Hz Transmitter Coil

25Hz Transmitter Coil

25Hz Transmitter Coil

Sullen Key Filter

Sullen Key Filter

Sullen Key Filter

Sullen Key Filter

RF Oscillator

DASH-7 Wireless Board

Altium PCB Design

Masters of Electronics Engineering

Arvostelut

Muutokset tallennettu

Näytetään 1 - 1 / 1 arvostelua

$50,00 USD

Verilog / VHDL

FPGA

•

Kokemus

Project Engineer

heinäk. 2015 - Voimassa

Embedded Systems design , FPGA and PIC Microcontroller based hardware design . Firmware and Software design and Systems analysis using Matlab.

Team Lead

tammik. 2012 - jouluk. 2014 (2 vuotta, 11 kuukautta)

I worked as Hardware Design group Team Lead , developed modules for wireless sensor network.

Digital and Analogue Design Engineer

toukok. 2010 - jouluk. 2011 (1 , 7 kuukautta)

FPGA Hardware Design of Satellite Communication system.

Koulutus

M.Sc Telecommunication Engineering

(2 vuotta)

MSc Electronics Engineering

(3 vuotta)

Pätevyydet

DSP Systems Engineering

University of California , Irvine

2012

Digital Signal Processing fundamentals, DFT,FFT , Digital Filter modelling and simulation using Matlab, FIR and IIR filter implementation on FPGA

Winner Best Design

Cypress Semiconductor

2004

Reconfigurable Logic using PSOC

Julkaisut

OTDR Implementation on FPGA

Embedded Strings (pvt)Ltd

Optical Time Domain Reflectrometery

In optical fiber communication, optical time domain reflectometery (OTDR) is a commonly used technique for characterization and fault location of optical fiber transmission systems. It involves measuring the fraction of a probe pulse that is scattered back (by Rayleigh scattering) from a silica fiber. Because of the very small levels of backscatter in single-mode fiber at long wavelengths, very sensitive optical detection is necessary to achieve adequate range performa

Audio Signal Processing

Ahmed A Ghouri

An audio signal frequency range is from 20Hz to 20Khz. In a music sample 20Khz bandwidth is required to encompass all harmonics. Although natural sounding speech only requires about 3.2Khz . Telecommunication systems typically operate with a sampling rate of about 8 kHz, allowing natural sounding speech, but greatly reduced music quality.

Here we are proposing a FPGA based audio signal filtering system which is reconfigurable and can be used as a Processing Engine to reduce background noise from a musi

Ota yhteyttä käyttäjään Elecguru011 työhösi liittyen

Kirjaudu sisään keskustellaksesi yksityiskohdista chatissa.

Varmennukset

Todistukset

Parhaat taidot

Selaa vastaavia freelancereita

Selaa vastaavia näyteikkunoita

Kutsu lähetetty onnistuneesti!

Kiitos! Olemme lähettäneet sinulle sähköpostitse linkin, jolla voit lunastaa ilmaisen krediittisi.

Jotain meni pieleen lähetettäessä sähköpostiasi. Yritä uudelleen.

Ladataan esikatselua

Lupa myönnetty Geolocation.

Kirjautumisistuntosi on vanhentunut ja sinut on kirjattu ulos. Kirjaudu uudelleen sisään.